Quick Links

Aims and Scope

The IEEE Journal on Exploratory Solid-State Computational Devices and Circuits focuses on multi-disciplinary research in solid-state circuits using exploratory materials and devices for novel energy efficient computation beyond standard CMOS (complementary Metal Oxide Semiconductor) technology. Focus is on the exploration of materials, devices and computation circuits to enable Moore’s Law to continue for computation beyond a 10 to 15 year horizon (beyond end of the roadmap for CMOS technologies) with the associated density scaling and improvement in energy efficiency.

Examples of appropriate topics to submit are:

- Quantum electronic devices (e.g., tunneling)

- Spintronics and Nanomagnetics devices

- Straintronics (piezo-electric) devices

- Plasmonics

- Functional materials

- High fan-in, fan-out logic circuits

- Reconfigurable and non-volatile computation circuits

- Computation circuits comprehending the on-chip communication means

This publication provides a unique interdisciplinary forum of scientists and engineers to critique and document progress in this field of promising alternatives to CMOS technology for computation devices, circuits and architecture.

Detailed Scope

The IEEE Journal on Exploratory Solid-State Computational Devices and Circuits (JXCDC) is designed for rapid publication of results across the areas of solid-state materials, devices, and circuits for novel computation (logic, memory, and communication) beyond the limits of conventional CMOS technology. The scope of the JXCDC is not limited to digital information processing, rather it also encompasses non-Boolean computation – including analog, neuromorphic computation, and novel concepts in computer automata. It is envisioned that these exploratory methods of computation could augment CMOS-based information processing.

Manuscripts are solicited in the areas of materials, devices, and circuits that transcend hierarchical boundaries to foster co-design enabling significant improvement in computational performance and energy efficiency. Manuscripts covering new materials must show a device application with computational performance impact. Manuscripts on devices must show potential to enable new integrated circuit architectures for improved computational performance and energy. Manuscripts on computation circuits and systems must be based on viable exploratory devices.

By its nature, the JXCDC is a publication that connects researchers across the design abstraction hierarchy of materials, devices, circuits, architectures, systems, and algorithms. It is a selective, archival publication that scientists and engineers can read to follow developments in beyond-CMOS technology for energy-efficient computation, and communication.

If your career involves work within the semiconductor industry or academia (scientists and engineers), the JXCDC will enable you to follow the developments and gain visibility beyond CMOS and the possible future direction of the integrated circuit and semiconductor industry. Also if you are a researcher in the integrated circuit and semiconductor industry or an academic institution, publication in the selective cross-disciplinary JXCDC should be considered so you contribute toward more energy efficient computation while elevating your career to new heights!

Paper Format Description

Papers can have 2 parts – the first part is a 4-8 page main paper (following a strict format – template available from website), and the second part is the supplementary material. The main paper itself will just focus on describing why the work is important, the state of the prior art, the key new accomplishment(s) or results, and then what the research directions are going forward. The main paper can have an accompanying supplementary material (detailed methods) part. The supplementary material is not mandatory, but authors are strongly encouraged to submit supplementary material, which will increase the chance of acceptance. The Supplementary material (detailed methods) will be peer reviewed along with the main paper. The ScholarOne website will have the guidelines for the two part submission – the main and the supplementary material.

JxCDC is an Open Access only Publication

Article Processing Charge (APC): US $1995 – effective 1 January 2024

Discounts:

- IEEE Members receive a 5% discount.

- IEEE Society Members receive a 20% discount.

These discounts cannot be combined.

For papers submitted in 2023, the Article Processing Charge (APC) is US$1950 plus applicable local taxes. The following discounts apply: IEEE Members receive a 5% discount. IEEE SSCS Members receive a 20% discount. Discounts do not apply to undergraduate and graduate students. These discounts cannot be combined.

Paper submissions must be done through the IEEE Author Portal website: www.ieee.atyponrex.com/journal/jxcdc

Guidelines for papers and supplementary materials, as well as a paper template, are provided at this website.

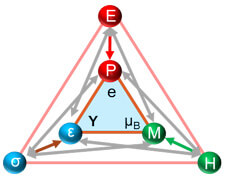

JxCDC is sponsored by:

- IEEE Solid-State Circuits Society

- Magnetics Society

- Circuits and Systems Society

- Electron Devices Society

- Council of Electronic Design Automation

- Council on Superconductivity

Accepted manuscripts will be posted in the IEEE Xplore website within 2 weeks after authors have correctly uploaded their final files in the IEEE Author Portal “Awaiting Final Files” queue.